## Lecture 3

# Verilator, Testbench and Vbuddy

Prof Peter YK Cheung Imperial College London

URL: <u>www.ee.ic.ac.uk/pcheung/teaching/EIE2-IAC/</u> E-mail: p.cheung@imperial.ac.uk

#### **Learning outcomes**

- Different types of simulators

- Verify a SystemVerilog (SV) module with Verilator

- Template for a Verilator testbench

- Using a shell script as shortcut

- Verify a SV module using gtkWave waveform viewer

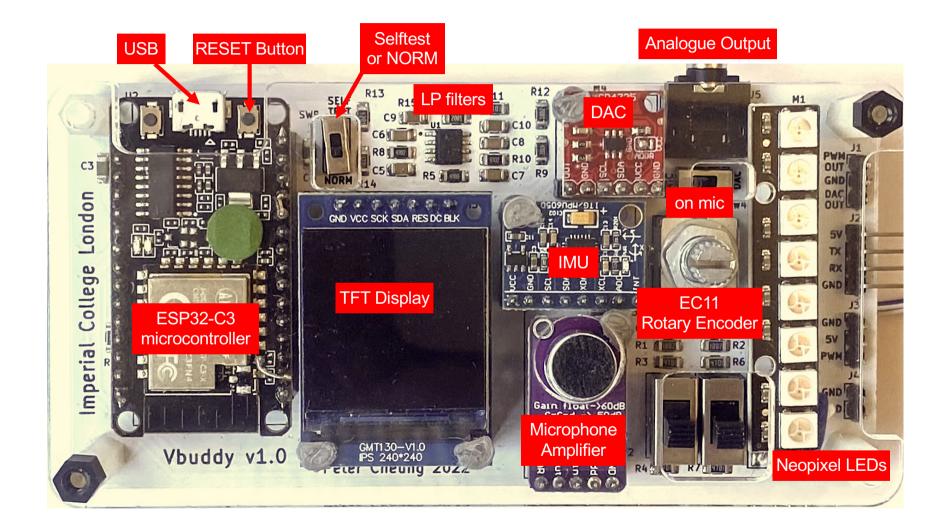

- Verify a SV module using Vbuddy

- What is in Lab 1?

Slides in this lecture are partly derived and modified from:

"Verilator: Fast, Free, But for me?", a talk by Wilson Snyder (created of Verilator) – http://www.veripool.org/papers

## **Verilator History**

- Verilator was born in 1994

- Verilog was the new Synthesis Language

- C++ was the Test-bench Language

- Paul Wasson synthesized Verilog into C++

- Wilson Snyder created Verilator since 2001

- Open-source and free

- Strong community with many contributors

- Works on all platforms (PC, Linux, MacOS)

- Fast, particularly with multithreading

### **Verilator User Base**

All trademarks registered by respective owners.

Users based on correspondence; there is no official way to determine "users" since there's no license!

## **Three types of simulator**

#### **1.** Instruction level simulator

- Processor instruction-level function

- No hardware representation, no concept of clock

- Written in high level language such as C or C++

- GNU RISC-V toolchain includes such a simulator

#### **2.** Cycle accurate simulator

- Simulate HDL specification of hardware, e.g. SystemVerilog

- All signal values correct cycle-by-cycle

- No time delay information

- Verilator is an example only two values: "0" or "1"

#### **3. Event-driven simulator**

- Change signal produces event in an event queue

- Simulate delay using timing model

- Capture glitches

- Slower and costly. Example: ModelSim

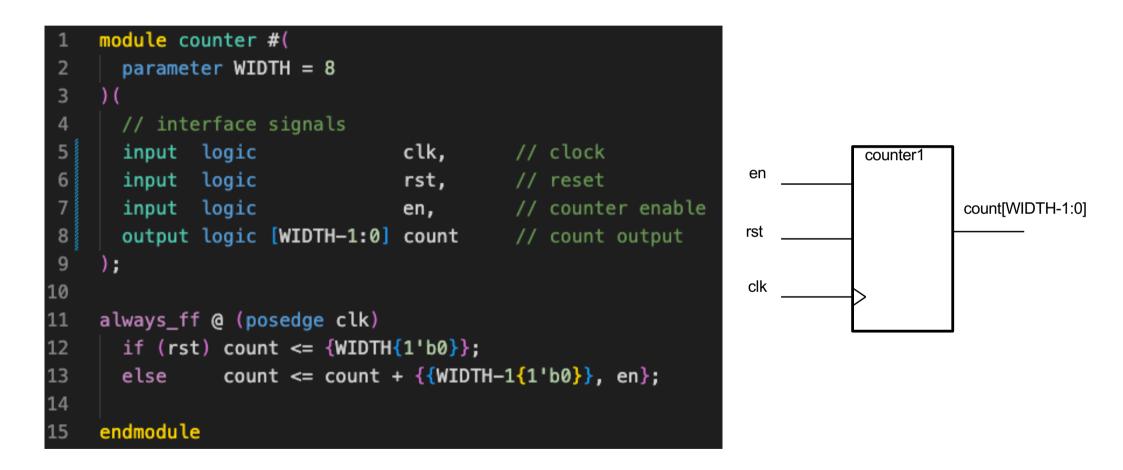

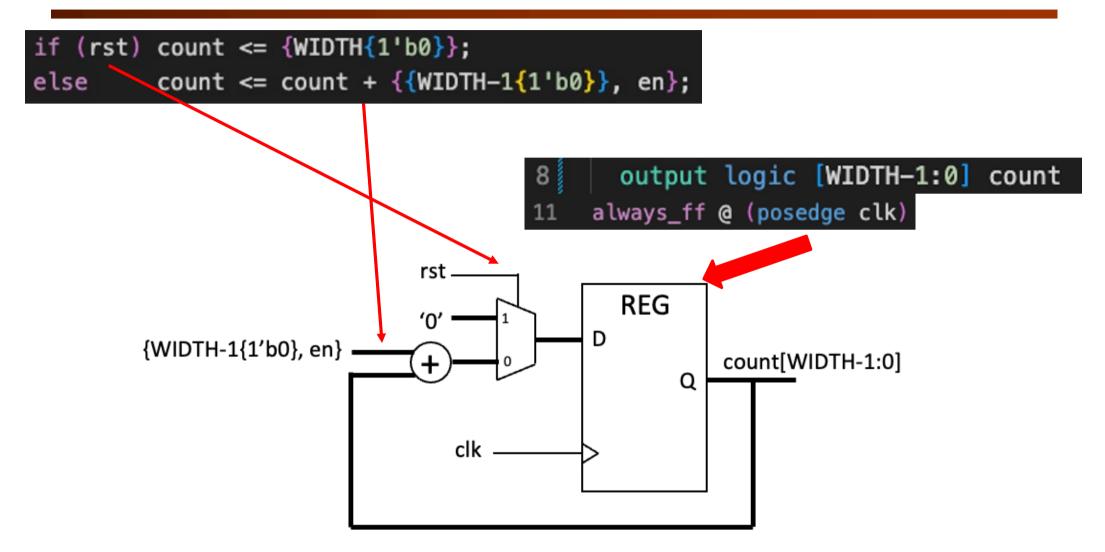

#### **Example: Simple Counter**

## Mapping from SV to hardware

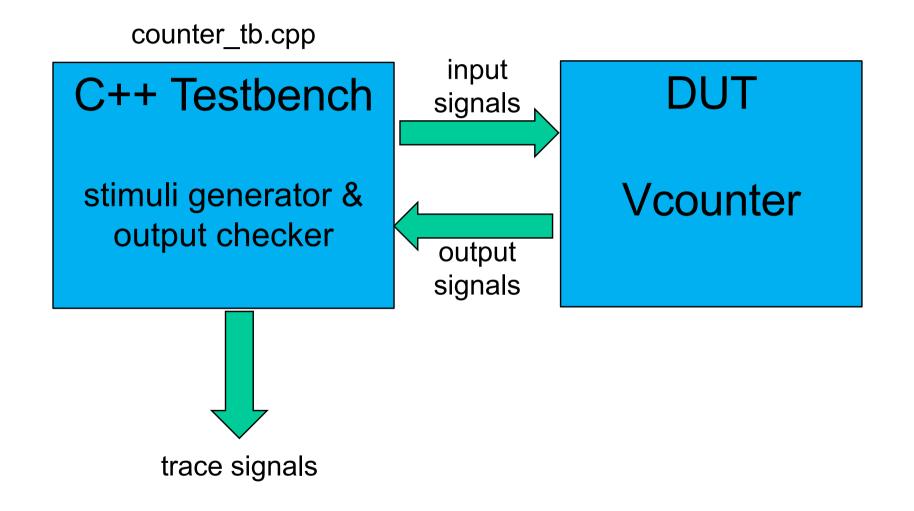

#### **Testbench**

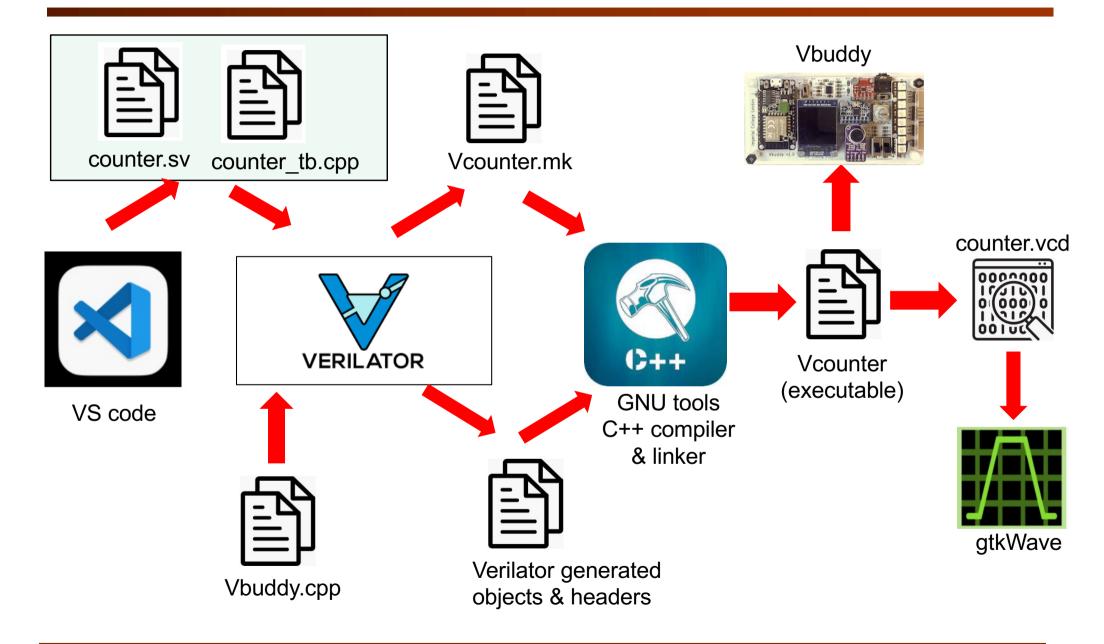

#### **How does Verilator work?**

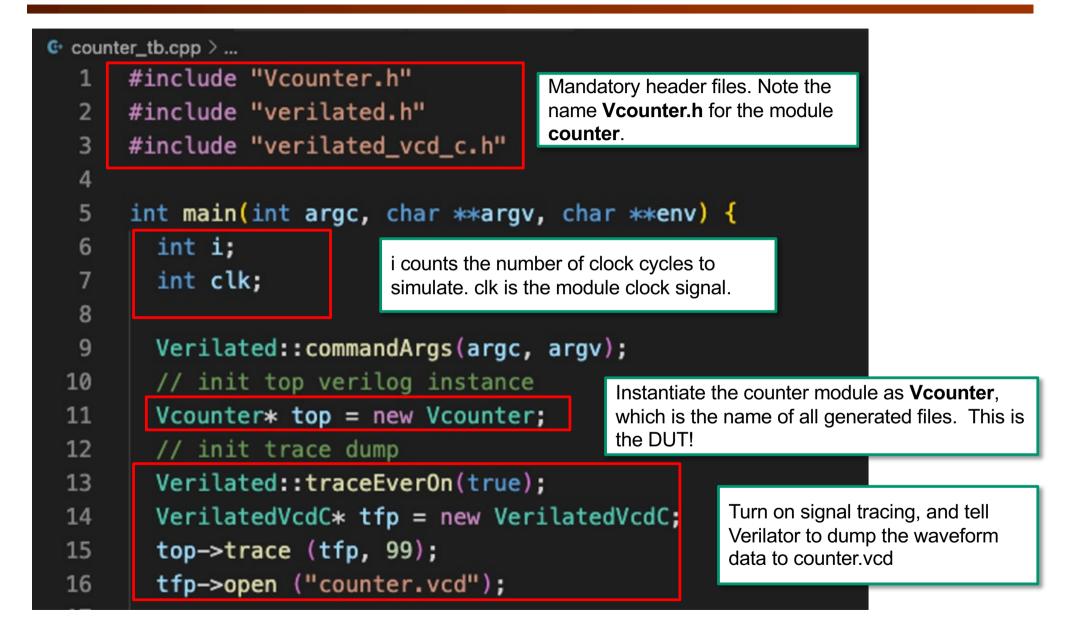

## Format of the Testbench (1)

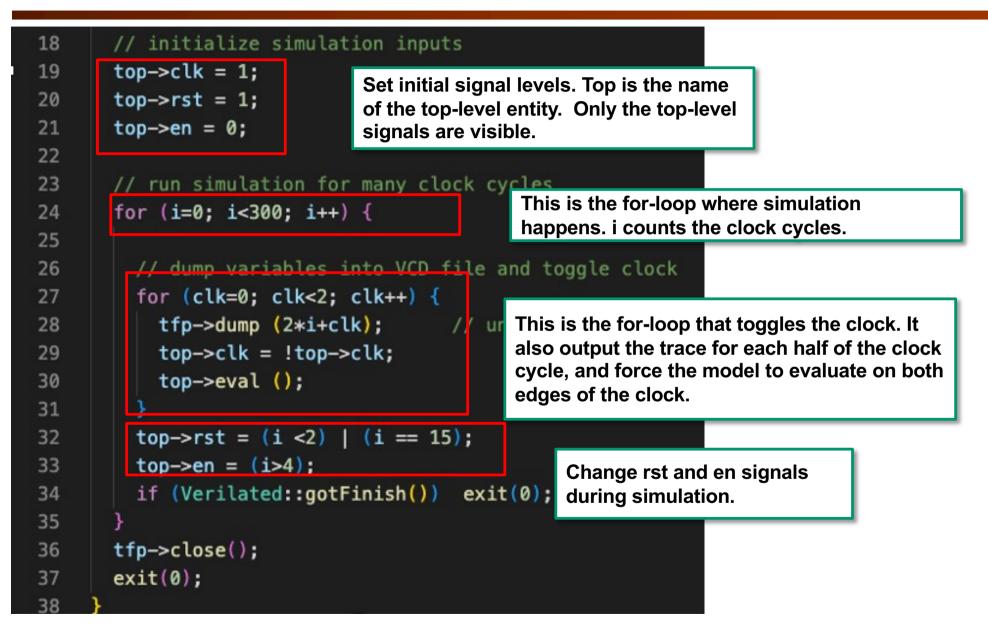

## Format of the Testbench (2)

### Making the final simulation model

```

$ doit.sh

#!/bin/sh

1

2

3

# cleanup

rm -rf obj_dir

4

rm -f counter.vcd

5

6

7

# run Verilator to translate Verilog into C++, including C++ testbench

8

verilator -Wall ---cc ---trace counter.sv --exe counter_tb.cpp

9

# build C++ project via make automatically generated by Verilator

10

make -j -C obj_dir/ -f Vcounter.mk Vcounter

11

12

# run executable simulation file

13

14

obj_dir/Vcounter

```

### Vcounter is the executable model of counter

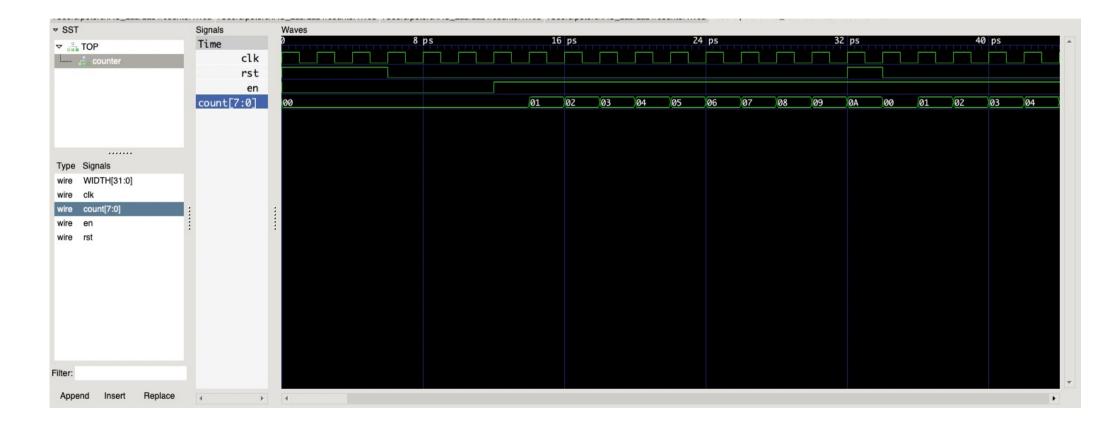

#### **Checking the simulation results**

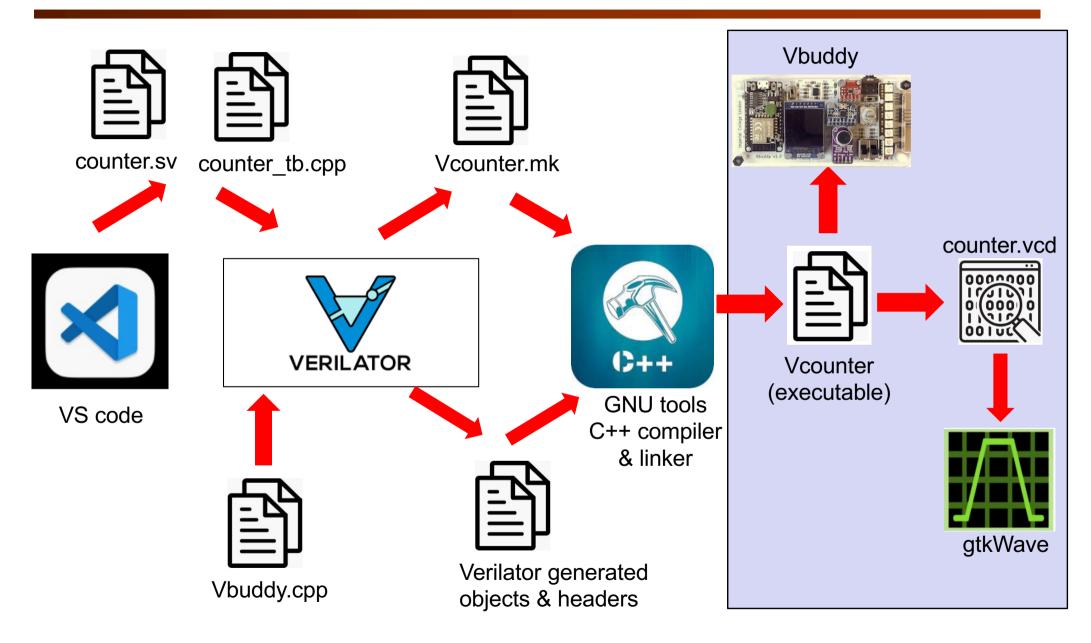

## Vbuddy